요즘 계속 보고있는 기업인데, 공부할 겸 블로그에 작성해봄

http://www.dms21.co.kr/new/main.html

DMS 살아숨쉬는 기업!

www.dms21.co.kr

https://www.youtube.com/watch?v=ain-1rs8mWk

- 코리아 써키트, 해성디에스, LG이노텍, 윈팩, SK하이닉스, SFA반도체 등 국내외 반도체 기업들의 의뢰로 PCB 최종검사를 진행 및 납품함(반도체 후공정)

- 2019년 보세공장 운영 특허 승인 : 보세공장은 외국물품이나 외국 물품과 내국물품을 원재료로 하여 제고, 가공 기타 이와 비슷한 작업을 하는 특허보세구역을 말함

https://www.customs.go.kr/kcs/cm/cntnts/cntntsView.do?mi=2844&cntntsId=831

관세청-보세공장 제도

보세공장제도 활용하세요. 보세공장 개요 보세공장은 외국물품이나 외국 물품과 내국 물품을 원재료로 하여 제조·가공 기타 이와 비슷한 작업을 하는 특허보세구역을 말합니다. 외국 원재료를

www.customs.go.kr

- 2019년 기업부설연구소 승인 : PCB 임가공과 관련한 다양한 연구개발

- PCB 외관 검사 -> 일반적인 CSP 제품, 검사 난이도가 높은 FCCSP, FCBOC, SOP, BOL, SIP 제품까지 세밀한 검사가 가능함

<코리아써키트 제품 소개 홈페이지 - 코리아써키트랑 협업한다고했으니까 맞는듯>

https://www.kcg.co.kr/kor/product/product.asp?catIdx=10

BOC - BOC - Package Substrate - 제품소개 - 코리아써키트

www.kcg.co.kr

CSP

CSP(Chip Size Package)는 Package Substrate 중에서 Substrate 의 크기가 반도체 Chip 크기의 120%를 넘지 않는 제품을 칭하는 표현입니다. 면적 축소를 위해 CSP는 일반적인 BGA에 비해서 배선 밀도가 조밀하게 형성됩니다. CSP의 가장 큰 목적은 실장면적의 축소에 있습니다.

FCCSP

FC-CSP(Flip Chip-CSP)는 Chip을 기판에 장착할 때, Chip이 뒤집어져서 장착되므로 여기에 기인하여 Flip Chip 이라고 합니다. 일반 CSP와 비교하여 반도체 Chip과 Substrate 간의 연결이 Wire-Bonding이 아닌 Bump로 이루어진다는 특성을 가지고 있습니다. Wire-Bonding이 필요하지 않기 때문에 일반적인 Wire-Bonding 공정을 거치는 제품들에 비하여 사이즈가 훨씬 작으며, Chip과 기판의 연결이 Wire-Bonding에서는 한번에 하나씩 붙이는 반면 Flip Chip에서는 동시에 수행할 수 있으며 연결되는 길이가 Wire-Bonding 보다 짧기 때문에 성능 또한 향상되는 점이 있습니다.>

BOC -> 여기서 FCBOC가 파생되지않았을까(추측)

BOC(Board on Chip)는 CSP 중에서 DDR2에 사용되는 제품을 칭하는 표현입니다. DRAM 패키징을 할 때 DDR2 부터는 Lead Frame 이 아닌 BGA를 사용하게 되었는데, 일반적인 BGA의 구조와는 조금 다르게 Chip이 거꾸로 실장되는 특성 때문에 BOC란 이름이 붙게 되었습니다. DDR2는 Chip의 I/O 부분이 일반적인 반도체와 달리 Chip 중앙에 배열되어 있기 때문에 Wire-Bonding이 이루어지는 부분도 Substrate 의 중앙에 위치합니다. DDR2에서 전통적인 메모리 모듈의 패키징 방식인 Lead Type을 사용하지 않고 BOC를 사용하는 것은 DRAM과 Substrate 간의 거리를 단축하여 신호손실을 최소화 하기 위해서입니다.

Sip

SIP(System In Package)는 하나의 패키지 안에 여러 개의 칩을 적층 또는 배열하여 하나의 독립된 기능을 가진 것을 말합니다. 마이크로프로세서를 포함해 여러 개의 칩으로 구성되는 완전한 시스템으로서의 모든 부분을 갖추고 있습니다. SIP는 개발 기간이 짧고 비용이 저렴하며, 다품종 소량 생산이 쉽고, 수율이 높은 장점이 있습니다. 그리고 여러 다른 기술들과 이종 부품들을 단일 패키지 위에 구현한 점에서 시스템 온 칩(SOC)과 구분되며, 또한 단독 시스템을 위해 개발된다는 점에서 MULTI CHIP Module과 구분됩니다.

- PCB 품질 보증(QA/QC)

1. IQA(수입검사, 수입품질보증) : 선행 예방 관리, FRONT 공정 FEED-BACK, 재발 방지 대책, 귀책 공정 제품 처리

2. MQC(재료?물질?검사? 품질관리) : 2D 설비 검출력 유지 관리, 2D 설비 재검증, ENGINEER 통보, 2D 검출력 향상 방안

3. VQC : 검사원 눈높이 상향 평준화, 검사원 OPL 교육, WORST 검사원 관리

4. FQC(Final Product QC) : 출하 품질 보증 공정 외 추가 불량개선, 자발적 개선 활동 _패킹을 진행하기 전에 모든 완제품을 점검

(검색해도 모르겠다...)

- 공정소개(Substrate : 기판(실리콘 웨이퍼) / 디스플레이용 유리판)

1. 3D AFVI : Substrate 표면 Bump의 Height, Diameter, Damage 등의 3D검사를 진행하는 3D AFVI공정

2. 2D AFVI : Substrate 표면을 조명으로 스캔하여 불량 유무를 확인하는 mono/Color 2D AFVI 공정

3. VRS : AFVI 설비에서 검출된 Substrate에 대한 Good, Bad unit을 판정하는 VRS 공정

4. FVI : Substrate 표면 외관 불량율 10배율~50배율 현미경으로 검사하는 FVI 공정

5. Laser Marking : Substrate 표면을 조명으로 스캔하여 확인된 불량 Unit에 Green Laser를 사용하여 불량 가공부를 표기하는 Laser Marking 공정

6. Rinse : DI.Water를 이용하여 Substrate 표면의 오염 및 이물질을 제거하는 Rinse 공정

7. N2 Bake : Substrate 표면의 습기를 제거하고, 질소를 투입하여 코팅하는 N2 Bake 공정

8. Warpage soter : Substrate의 휨을 측정하고 선별하는 Warpage soter 공정

9. Auto sorting : Substrate를 광학 스캔하여 불량 Unit의 개수를 자동 선별하는 Auto sorting 공정

10. Packaging : 최종 선별 및 패키징하는 공정

+ All process 2D map system : 업무 내용들이 2D 캐드도면에 잘 정리되어있단 얘기인듯

+ Clean booth에서 패키징

+ MES(제조실행시스템_아래 소개링크)를 통한 모니터링

http://www.xnsolution.co.kr/smart/mes_03.php

엑센솔루션

품질규격, 공정조건 SPC 관리 기반의 사전품질관리 확보 고객사의 품질경영 대응( SQ인증 심사 대응 )을 위한 품질 측정 Data 자동화 연계한 SPC 시스템 구현 초종종 검사 품질에 대한 검사이력 및 SP

www.xnsolution.co.kr

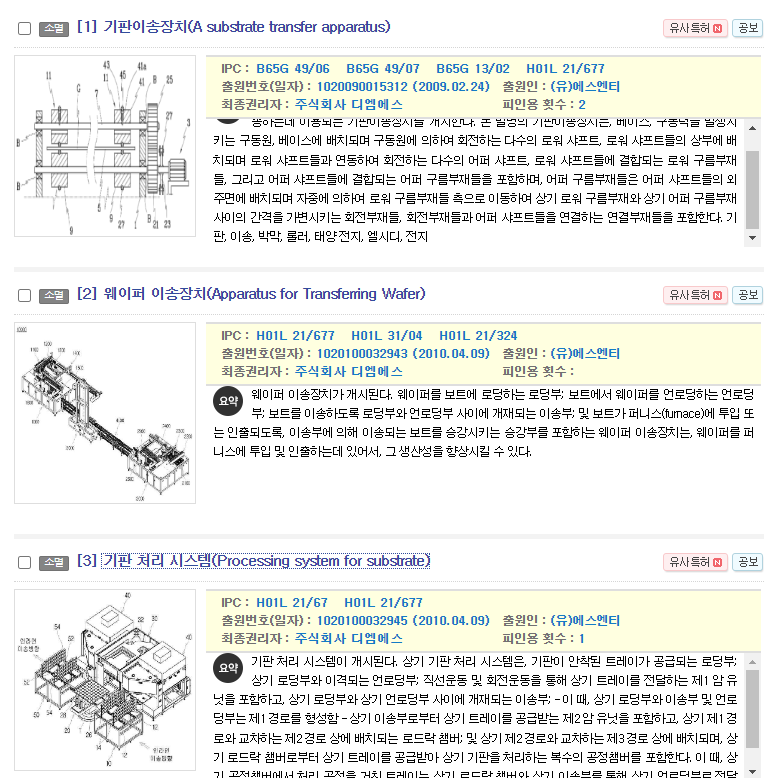

-키프리스를 통해 검색된 DMS 지식재산권 목록

(경험담)키프리스(특허검색무료사이트)를 활용한 지식재산권 직무 면접준비

지식재산권, IP, 특허 관련해서 면접을 볼 예정인 사람들을 위해 글을 남긴다. (서류는 합격하고, 면접) 면접을 보기전, 회사와 직무에 대해 많이 조사해가자(면접 기본팁) 회사보다는 '지식재산

mosunji.com

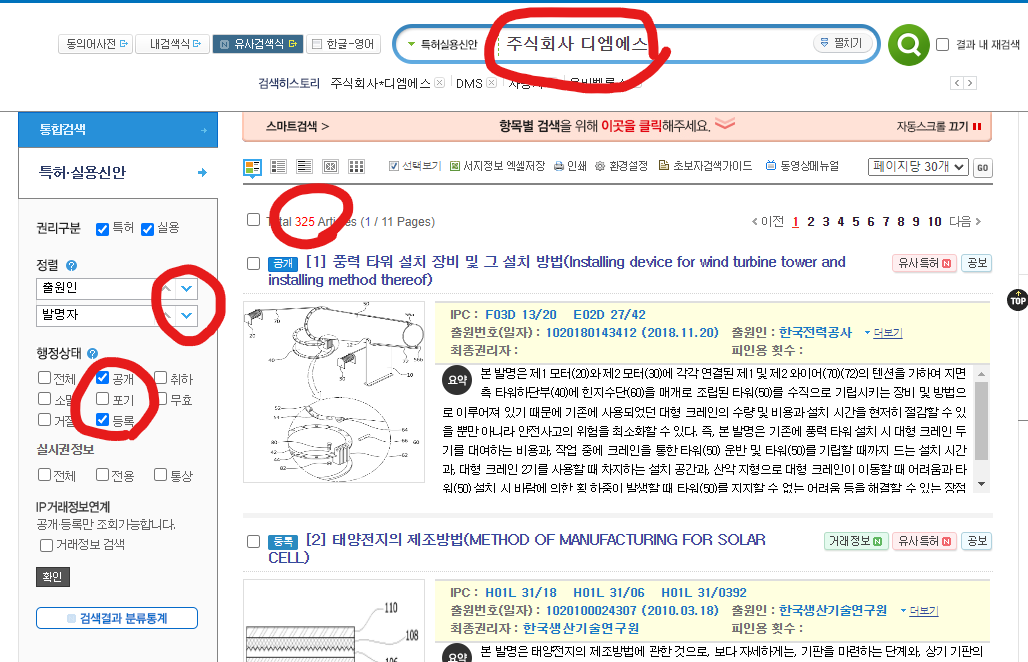

: 참고로 검색시 왼쪽에 특허/실용신안으로 클릭하고 / 정렬을 '출원인' , '발명자'로 세팅하고 오름차순으로 표기하고 / 검색했음 -> 검색결과물이 8,200개라..

연차료(등록료)를 내다가 안내서 소멸된것으로 확인됨

공개, 등록에만 체크하고 / 내림차순 / '주식회사 디엠에스'라고 다시 검색함 325개의 특허 검색

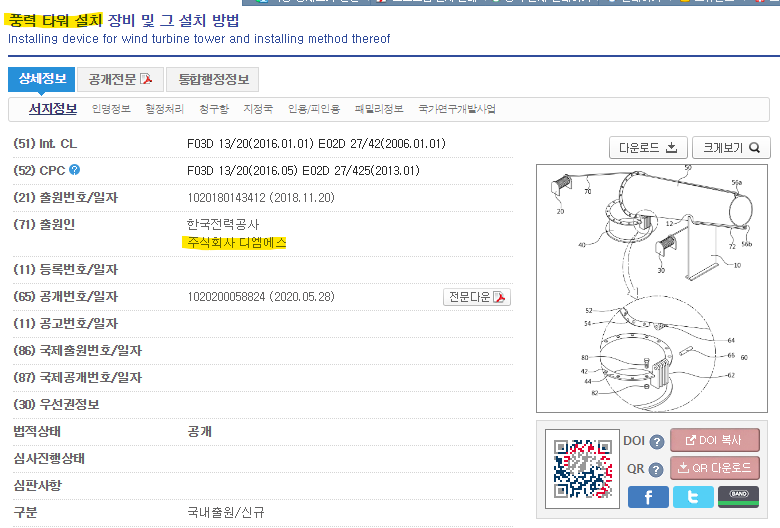

이번에 한국전력이랑 풍력타워 설치관련 사업 같이 진행한다더니 지식재산권이 맨 위에 있음

내리다보니

반도체 후공정 패키징과 관련된 용어와 지식재산권이 등록된것으로 보임

처음엔 진짜 이해안됬는데, 그래도 반도체를 좀 공부하고 오니까 약간은 무슨말인지 이해가 된다..

좀더 보면서 중간중간 내용 추가할 예정

반도체 기업 면접/투자를 위한 '반도체 기본 지식 공부' 1탄(기본편)

반도체 기업의 '지식재산권 관리' 파트에 지원을 했고, 서류가 통과되어 면접을 가게되었음. 그래서 해당 기업의 소개 영상, 뉴스, 자료들을 찾아봤는데.. 반도체에 대해 모르니 뭔말인지 모르겠

mosunji.com

반도체 기업 면접/투자를 위한 '반도체 기본 지식 공부' 1탄(기본편)

반도체 기업의 '지식재산권 관리' 파트에 지원을 했고, 서류가 통과되어 면접을 가게되었음. 그래서 해당 기업의 소개 영상, 뉴스, 자료들을 찾아봤는데.. 반도체에 대해 모르니 뭔말인지 모르겠

mosunji.com

'억지로 공부(면접, 이직, 투자관련)' 카테고리의 다른 글

| (경험담)키프리스(특허검색무료사이트)를 활용한 지식재산권 직무 면접준비 (0) | 2023.07.04 |

|---|---|

| 빙그레가 이런 기업이었어?(빙그레 기업분석) (0) | 2023.06.22 |

| 유비벨록스(주) 뭐하는 회사야?_팅크웨어, 유플래너, 에그, 마이데이타 (0) | 2023.06.22 |

| 반도체 기업 면접/투자를 위한 '반도체 기본 지식 공부' 2탄(심화편) (0) | 2023.06.11 |

| 반도체 기업 면접/투자를 위한 '반도체 기본 지식 공부' 1탄(기본편) (0) | 2023.06.11 |

댓글